新着情報

平成28年度卒業研究紹介「モデル計算機KERNELの更新における通信機構の実装」

発表者:武藤 匠汰(情報科学科)/指導教員:澤田 直 准教授

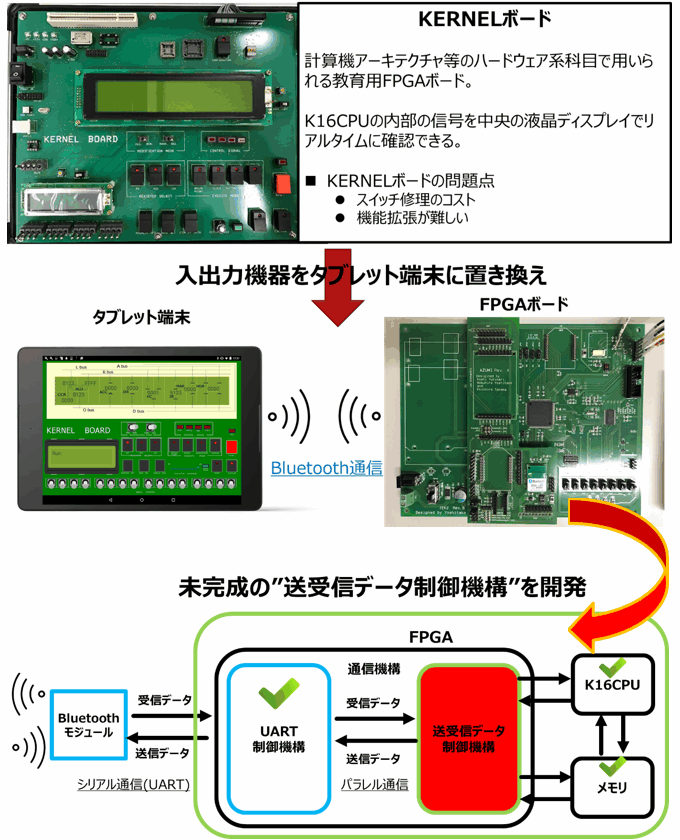

モデル計算機KERNELは、本学のハードウェア系科目で一貫して利用されている教材である。そのハードウェアモデルであるKERNELボードは、老朽化が進んだことにより継続使用が困難となったため、平成26年度より新しいKERNELボードの開発が始まった。

更新が必要となった要因は主に、FPGAの開発を最新のPCで行えなくなったこと、スイッチ修理等によるコスト負担が大きいことである。新KERNELボードではコスト削減の為に、LCD・スイッチ等の入出力機器をタブレット端末に置き換える。その為には、タブレット端末とのデータ送受信を制御する通信機構を新規に開発する必要がある。

前任者の研究により、FPGA内部はCPU、メモリ、通信機構の3つの要素で構成されている。この中で、CPUとメモリのモジュールは統合され、FPGA上での動作確認が行われたが、通信機構の一部機能が未完成であり、実機上での動作確認には至っていない。また、各モジュールが必要とするFPGAのリソース数が実際のリソース数よりも多く、FPGA上に全モジュールを実装できない問題が発生している。

本研究では通信機構を完成させ、新KERNELボード上に実装することを目的とする。通信機構を実装するために、タブレット端末との通信規約の策定と、各モジュールの容量圧縮を行う。現状の通信機構は、タブレット端末側と異なる通信規約に沿って開発を進めているため、共通の通信規約を策定する。その際、通信機構のリソース使用率を考慮して、データの識別方法と応答信号に関する変更を行う。また、完成済みのモジュールに対しても容量圧縮のための修正と機能の絞り込みを行い、ボード上に新しいKERNELの全モジュールを実装する。

通信機構を完成させることで、実機による動作検証が可能となる。実機検証では全スイッチ入力、タブレット端末とFPGA間のCPU状態同期について検証を行い、正常に動作することを確認する。

この卒業研究は平成28年度情報科学部優秀卒業研究に選出されました。

(2017/02/02 掲載。記載内容は執筆当時のものです)